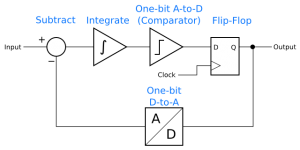

Not only are delta-sigma techniques at the root of many of today’s analog-to-digital converters (ADC) and digital-to-analog converters (DAC), what they reveal about the relationship between sample rate, bandwidth, and resolution lies near the heart of the multirate techniques popular in modern digital signal processing (DSP) systems.

Not only are delta-sigma techniques at the root of many of today’s analog-to-digital converters (ADC) and digital-to-analog converters (DAC), what they reveal about the relationship between sample rate, bandwidth, and resolution lies near the heart of the multirate techniques popular in modern digital signal processing (DSP) systems.

This multi-part series of tutorials will work its way from the basics of delta-sigma data converters to more advanced techniques, with an approach that values intuition as much as math. The series is a work in progress, so please subscribe via Atom or RSS or check back regularly for future installments.

- Part 1: Introducing the Delta Sigma Modulator (31-May-2011)

- Part 2: The Anti-Aliasing Advantage (23-July-2011)

- Part 3: The controls-system perspective (4-July-2012)

Hi,

at first i wanted to thank you for this article.

But there is one little question to be left.

Is it really necessary to put an anti aliasing filter in front of the DS-Modulator?

Isn’t it possible to filter out all not wanted signal parts with the integrator?

Thanks

Andreas

Hi, Andy.

It took me a while to reply because I wanted to think the answer through. In an ADC with a continuous-time loop filter (integrator), yes, you can build a delta-sigma modulator without an additional anti-aliasing filter. However, nearly all delta-sigma ADCs use switched-capacitor techniques for their loop filters. If your ADC uses switched capacitors, you will still need an anti-aliasing filter.

Even with a continuous-time loop filter, using the loop filter for anti-aliasing constrains the design of the ADC. Depending on what kind of digital filter follows the modulator, you may need anti-aliasing for the ADC’s output sample rate, which is quite a bit lower than the modulator’s sample rate. Doing some of the filtering in an anti-aliasing filter may permit using a simpler digital filter.

Stephen

Dear sir,

Please give me an outline or lecture about 1.8-V digital audio sigma delta modulator in 0.8 m cmos

With pictures. Thanks

Hello, sir.

Unfortunately, I do not have such notes or lectures to share. I’d suggest doing some searches on Google Scholar or the IEEE web site for published papers on delta-sigma in 0.8 ㎛. I’ve never worked on one, but I have no doubt you will find relevant papers in JSSC.

Stephen

Hi!

The explanation was very clear and I enjoyed reading it very much!

I have a question though, I looked at many papers dealing with Sigma-Delta ADC and none of them showed the simple implementation of counter as the LPF and Decimation blocks.

All the work I could find had much more complex FIR filters instead of the simple counter (which actually behaving like FIR with only 1’s as its multipliers).

Have you read any paper using the technique you used (with counter)? Or can you please direct me to somewhere I should look? (looked at IEEE explore)

Thanks!

Hi, Tom!

I described a counter here because it helps build intuitive understanding. Counters generally aren’t used is because they allow excessive amounts of high frequency content to be aliased into the passband. A well-designed filter will reduce that high-frequency content better, reducing the amount of high-frequency noise that gets aliased down and thus improving the signal-to-noise ratio of the delta-sigma converter.

Here’s a way to think of it: The output of the counter, sampled and reset every N delta-sigma samples, is identical to an N-sample moving-average filter sampled at the same rate. The moving-average filter is the sum of the previous N samples, and the counter is the count of those samples, so if we’re talking about 1’s and 0’s, they are the same thing. If you look up the spectral characteristics of a moving-average filter, you will see that they have periodic “bumps” in their stop band where they let more power through. That’s high-frequency noise that we don’t want, and the down-sampling process will alias that noise down on top of the signal we do want.

Also, using a counter really limits the design freedom. If one uses a filter instead, that high-frequency noise can be greatly reduced, which in turn means less noise on top of the desired signal. The end result is that you can get more meaningful bits out of the ADC. And that’s why you don’t see commercial delta-sigma converters using a counter instead of a filter.