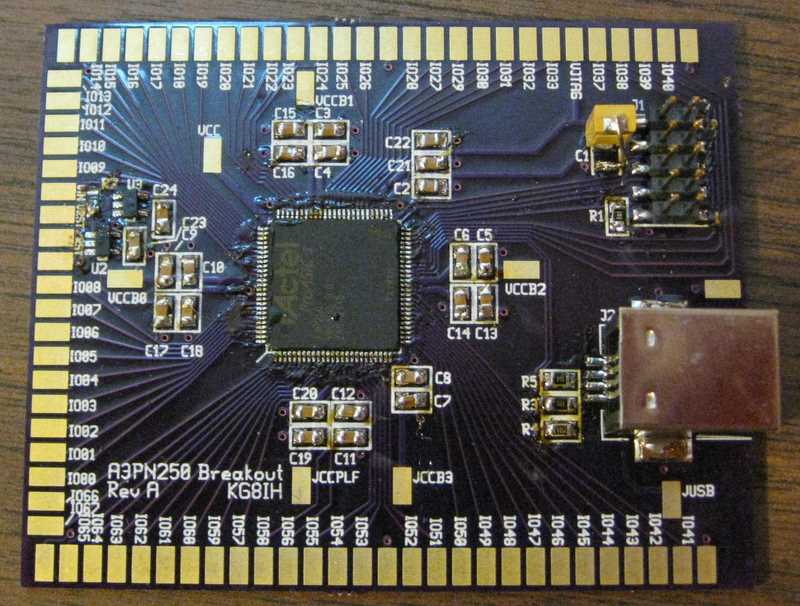

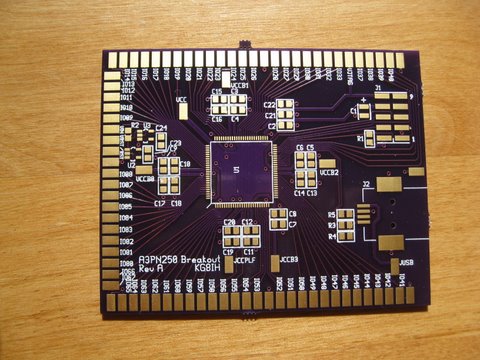

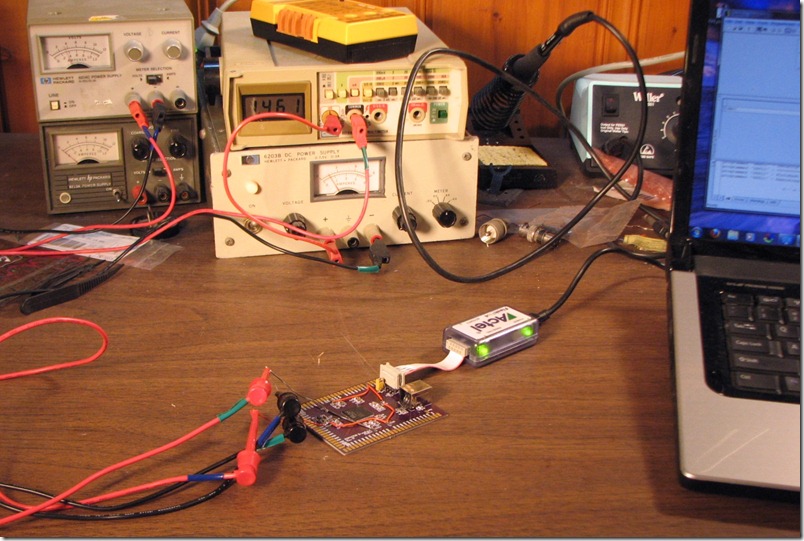

There comes a point in any project when one has to find out if it works, but first, there is the “smoke test”: Turn on the power and see if anything goes up in smoke. I smoke tested the A3PN250 FPGA breakout board this weekend, and it passed, or at least it failed to emit smoke. In any event, no smoke was emitted and the board survived. In fact, the board works. I talked to the board with a FlashPro4 programming pod and my rewired JTAG cable. The FPGA passed the pod’s signal-integrity check and identified itself correctly, so it is certainly alive.

I follow a few rules of thumb when smoke testing. These aren’t things one learns in books, but instead from other engineers, so they are worth writing down and passing on. Continue reading “Smoke testing the A3PN250 FPGA board”