If my goal is to build an FPGA-based ham radio, one of the modules I can’t do without is an iambic keyer. I have to confess that I have never been much of a CW (Morse code) operator, but with so many logic gates available, it would be a shame to leave out a keyer.

The basic idea behind an iambic keyer is to use a two-lever “paddle” to send Morse code. Pressing one paddle, usually with the thumb, sends a series of dits (dots), and pressing the other paddle, usually with the index finger, sends dahs (dashes). Squeezing both paddles alternates between dits and dahs. The didahdidahdidah… sound of squeezing the paddles sounds a bit like the iambic feet of English poetry, hence the name “iambic keyer”. If Shakespeare were a Morse code operator, one of his sonnets might include the sweet iambic pentameter “didahdidahdidah, didah didah!”

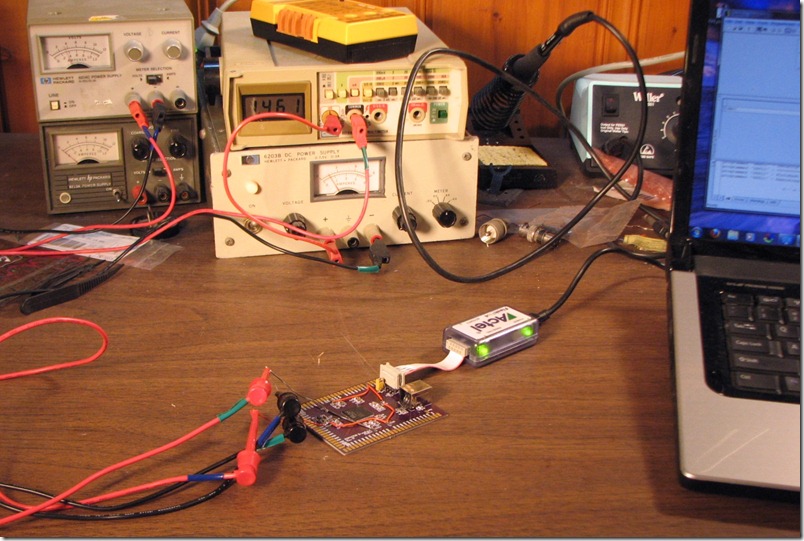

Writing an iambic keyer turned out to be a good way to get the kinks out of the FPGA toolchain. The code itself is pretty simple and straightforward. One flip-flop keeps track of whether the current symbol is a dit or a dah. Another tracks whether the paddle for the opposite symbol (dah or dit, respectively) has been pressed during the current symbol. Finally, a two-level counter handles the timing of the dits and dahs and operates the key line. There is a simple sidetone, too. Continue reading “Iambic keyer in Verilog”